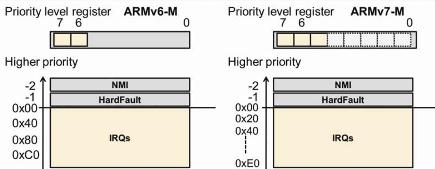

CortexM Interrupt Process (much of this is transparent when using C) 1 Interrupt signal detected by CPU 2 Suspend main program execution finish current instruction save CPU state (push registers onto stack) set LR to 0xFFFFFFF9 (indicates interrupt return) set IPSR to interrupt number load PC with ISR address from vector table 3DOCUMENTATION MENU DEVELOPER DOCUMENTATION Back to searchNov , 15 · modules' hardware consists of an ARM Cortex M4 host processor, Broadcom Annex A, Table A1, EN Requirements Table (ENRT) reproduced below as Table 1 herein Only Reference Items 1 through 9 are addressed in this report for Transmitters, since this report covers only the NFC Transmitter

Arm Explains Good Interrupt Control For Low Power Processors